# ESNOG-32 400G And Beyond

Manuel Mendez Systems Engineering manuel@

Confidential. Copyright © Arista 2024. All rights reserved.

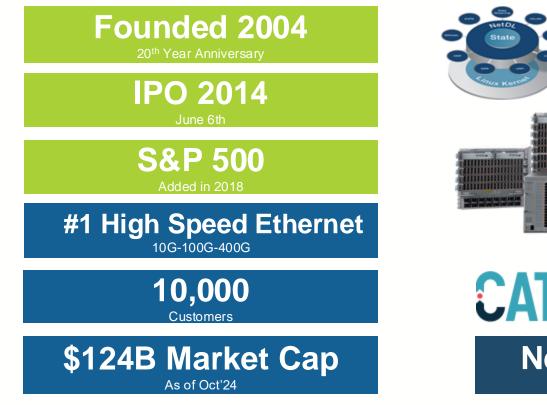

#### About Arista Networks

CATNIX Catalonia Neutral Internet Exchange

### **Network Provider**

Since 2016

#### Agenda

Transceivers 101

Switch Silicon & Optics Evolution

400G

800G and 1.6Tbps

LPO Optics

#### Disclaimer

The examples provided in the presentation are for illustration purposes ONLY, and are NOT indicative of ALL Arista's shipping products.

Any information contained in this presentation regarding third parties has been obtained from publicly available sources.

# **Transceivers 101**

Refresher, Breakouts and Gearboxes

Confidential. Copyright © Arista 2024. All rights reserved.

#### Refresher

\*Serializer Deserializer \*\*Physical Layer device \*\*\*Multi-Source Agreement

- Transceivers convert a host-side (internal) signal to the line-side (external) signal

- Host-side interfaces are known as SerDes\*

- Defined by IEEE standards

- Designed for short range high speed signalling (i.e. chip to chip)

- Connect the PHY\*\* to the transceiver.

- PHY may be inside the switching silicon or an external component (e.g. Base-T PHY)

- Line-side interfaces may be electrical or optical

- Defined by IEEE standards or by industry groups (e.g. 10G-LR)

- Transceiver format and electrical interface design

- Physical form factor, electrical interface defined by MSA\*\*\*

- Internal implementation is the vendor's secret sauce

To interoperate with hosts and link partners, transceivers must meet many common standards

Host

Line

Host Side (Electrical) Line Side (Optical or Electrical)

| Transceiver Format                                                                                          | Host Side Interface<br>(aka SerDes) | Example Type | Line Side Interface                           |  |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------|-----------------------------------------------|--|

| SFP+<br>(Small Form factor Pluggable +)                                                                     | 1 x 10Gbps                          | 10G-SR       | 1 x 10G wavelength<br>(on single MMF pair)    |  |

| SFP+<br>(Small Form factor Pluggable+)                                                                      | 1 x 10Gbps                          | 10G-T        | 1 x Cat5e or better                           |  |

| SFP28<br>(Small Form factor Pluggable 28Ghz)                                                                | 1 x 25Gbps                          | 25G-SR       | 1 x 25G wavelength<br>(on single MMF pair)    |  |

| SFP28<br>(Small Form factor Pluggable 28Ghz)                                                                | 1 x 25Gbps                          | 25G-LR       | 1 x 25G wavelength<br>(on single SMF pair)    |  |

| SFP-DD or DSFP<br>(Small Form factor Pluggable + Double Density)<br>(Double SFP is an alternative standard) |                                     | 100G-DR      | 1 x 100G wavelength<br>(on a single SMF pair) |  |

Transceiver format defines the host-side electrical characteristics, line side varies by use case

Host Side (Electrical) Line Side (Optical or Electrical)

| Transceiver Format                                 | Host Side Interface<br>(aka SerDes) | Example Type | Line Side Interface                              |

|----------------------------------------------------|-------------------------------------|--------------|--------------------------------------------------|

| QSFP+<br>(Quad Small Form factor Pluggable +)      | 4 x 10Gbps                          | 40G-SR4      | 4 x 10G wavelengths<br>(on 4 parallel MMF pairs) |

| QSFP+<br>(Quad Small Form factor Pluggable +)      | 4 x 10Gbps                          | 40G-LR4      | 4 x 10G wavelengths<br>(on a single SMF pair)    |

| QSFP28<br>(Quad Small Form factor Pluggable 28Ghz) | 4 x 25Gbps                          | 100G-SR4     | 4 x 25G wavelengths<br>(on 4 parallel MMF pairs) |

| QSFP28<br>(Quad Small Form factor Pluggable 28Ghz) | 4 x 25Gbps                          | 100G-LR4     | 4 x 25G wavelengths<br>(on a single SMF pair)    |

| QSFP28<br>(Quad Small Form factor Pluggable 28Ghz) | 4 x 25Gbps                          | 100G-DR      | 1 x 100G wavelength<br>(on a single SMF pair)    |

Transceiver format defines the host-side electrical characteristics, line side varies by use case

Lina Cida

| (Electrical)                                                                |                                     | LINE SIDE<br>(Optical or Electrical) |                                                      |  |

|-----------------------------------------------------------------------------|-------------------------------------|--------------------------------------|------------------------------------------------------|--|

| Transceiver Format                                                          | Host Side Interface<br>(aka SerDes) | Example Type                         | Line Side Interface                                  |  |

| QSFP56<br>(Quad Small Form factor Pluggable 56Ghz)                          | 4 x 50Gbps                          | 200G-LR4                             | 4 x 50G wavelengths<br>(on a single SMF pair)        |  |

| QSFP-DD/QSFP56-DD<br>(Quad Small Form factor Pluggable - Double<br>Density) | 8 x 25Gbps or<br>8 x 50Gbps         | 2 x 100G or 2 x 200G<br>DAC          | 2 x (4 x 25G) electrical<br>2 x (4 x 50G) electrical |  |

| QSFP-DD/QSFP56-DD<br>(Quad Small Form factor Pluggable - Double<br>Density) | 8 x 25Gbps or<br>8 x 50Gbps         | 400G-SR8                             | 8 x 50G wavelengths<br>(on 8 parallel MMF pairs)     |  |

| QSFP-DD/QSFP56-DD<br>(Quad Small Form factor Pluggable - Double<br>Density) | 8 x 50Gbps                          | 400G-DR4                             | 4 x 100G wavelengths<br>(on 4 parallel SMF pairs)    |  |

| OSFP<br>(Octal Small Form factor Pluggable)                                 | 8 x 50Gbps                          | 400G-LR4                             | 4 x 100G wavelengths<br>(on a single SMF pair)       |  |

| OSFP<br>(Octal Small Form factor Pluggable)                                 | 8 x 50Gbps                          | 400G-ZR                              | 1 x 400G wavelength<br>(on a single SMF pair)        |  |

Lloot Cido

### Physical Link Naming Convention

| Nomenclature | Link Speed | Underlying Carrier(s) | Example Deployment                                |

|--------------|------------|-----------------------|---------------------------------------------------|

| 50G-2        | 50G        | 2 x 25G NRZ           | 50G on 2 lanes of a QSFP28                        |

| 50G-1        | 50G        | 1 x 50G PAM4          | 50G on 1 lane of an SFP-DD / QSFP56 / Q-DD / OSFP |

| 100G-4       | 100G       | 4 x 25G NRZ           | 100G on 4 lanes of a QSFP                         |

| 100G-2       | 100G       | 2 x 50G PAM4          | 100G on 2 lanes of an SFP-DD / QSFP56 / DD / OSFP |

| 100G-1       | 100G       | 1 x 100G PAM4         | 100G on 1 lane of a QSFP112 / DD112 / OSFP800     |

| 200G-4       | 200G       | 4 x 50G PAM4          | 200G on 4 lanes of a QSFP56 / DD / OSFP           |

| 200G-2       | 200G       | 2 x 100G PAM4         | 200G on 2 lanes of a QSFP112 / DD112 / OSFP800    |

| 400G-8       | 400G       | 8 x 50G PAM4          | 400G on 8 lanes of a QSFP-DD / OSFP               |

| 400G-4       | 400G       | 4 x 100G PAM4         | 400G on 4 lanes of a QSFP112 / DD112 / OSFP800    |

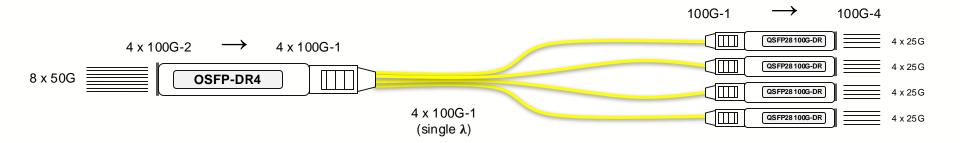

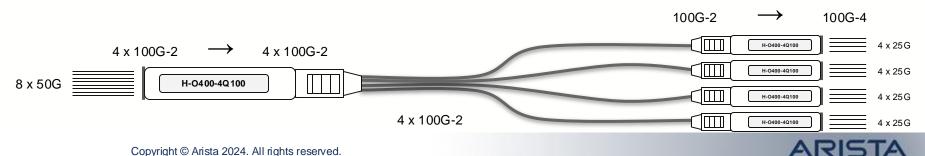

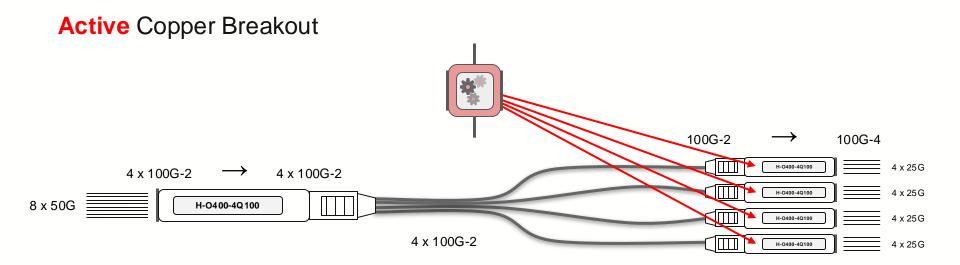

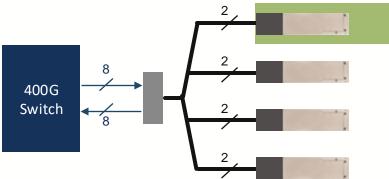

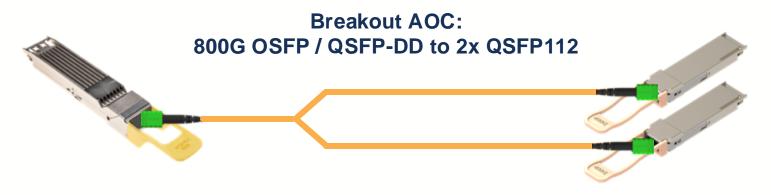

#### **Breakouts**

**Optical Breakout**

Active Copper Breakout

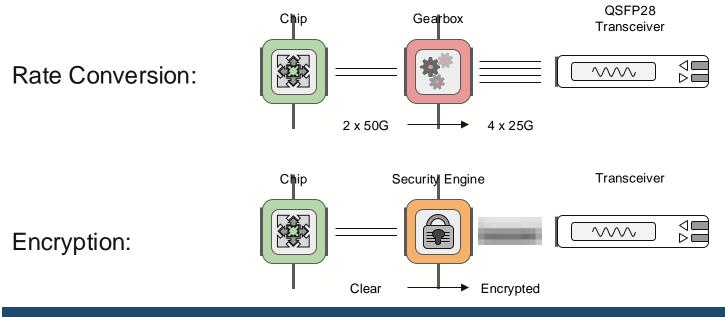

Provides rate conversion and may add other features:

Gearbox converts 2 x 50G to 4 x 25G to support QSFP28

ARISTA

#### ARISTA

Founding Member

# Switch Silicon & Optics Evolution

Confidential. Copyright © Arista 2024. All rights reserved.

#### Switch Silicon Bandwidth Evolution

ARISTA

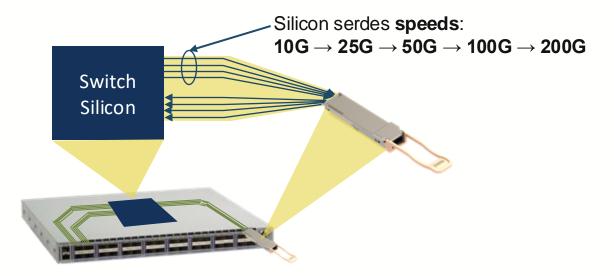

#### What Limits Switch Silicon Bandwidth?

Switch silicon bandwidth is constrained by two fundamental factors:

- 1. Number of I/O on a silicon die

- 2. How fast the I/O (SerDes) can be driven

The easiest way to go faster is (for SerDes speeds) to go faster

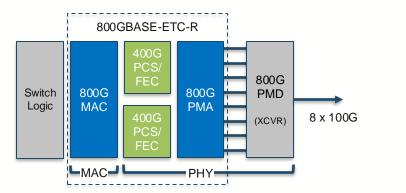

### State of 800/1.6 TGbE

- 800 GbE Requirements:

- 100G SerDes

- 800G Transceivers

- 800G MAC Layer

#### Founding Member

| Standard                                            | Status                 | Description                                                     | Electrical Interfaces              | Silicon  |

|-----------------------------------------------------|------------------------|-----------------------------------------------------------------|------------------------------------|----------|

| IEEE 802.3ck                                        | Sept 2022              | 100, 200 & 400 GbE using 100G lanes                             | 100G-1, 200G-2,<br>400G-4          | Shipping |

| Ethernet Technology<br>Consortium<br>800GBASE-ETC-R | October 2020           | 800G using 100G lanes                                           | 800G-8                             | Shipping |

| IEEE 802.3df                                        | March 2024<br>Approved | 800G using 100G lanes                                           | 800G-8                             |          |

| IEEE P802.3dj                                       | 2H 2026                | 200, 400 Gb/s, 800 Gb/s, and<br>1.6 Tb/s using 200 Gbit/s lanes | 200G-1, 400G-2,<br>800G-4, 1600G-8 | Future   |

|                                                     |                        | 1.6 Tbps MAC                                                    | · · ·                              |          |

### **Optics Form factors**

Transition from 400G QSFP-DD to 800G OSFP. Why?

- Better thermal performance (integrated heatsink, larger surface area)

- Robust signal integrity (single row connector)

- Better fit for dual-LC connectors for 800G

- Industry aligning with largest volume consumers

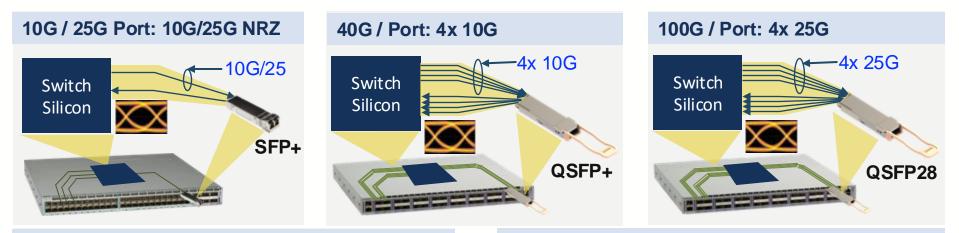

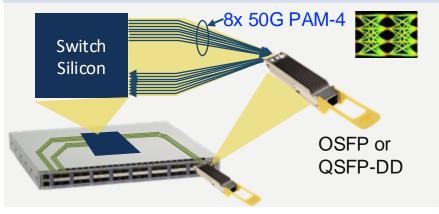

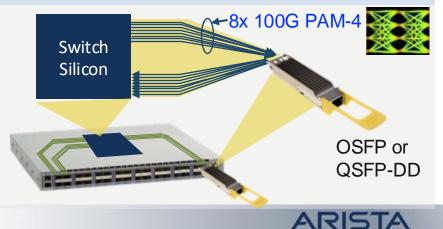

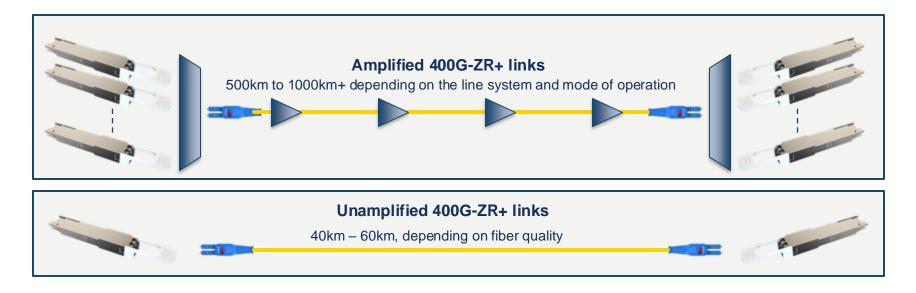

#### SerDes Speed Transition

#### 400G / Port: 8x 50G PAM-4

#### 800G / Port: 8x 100G PAM-4

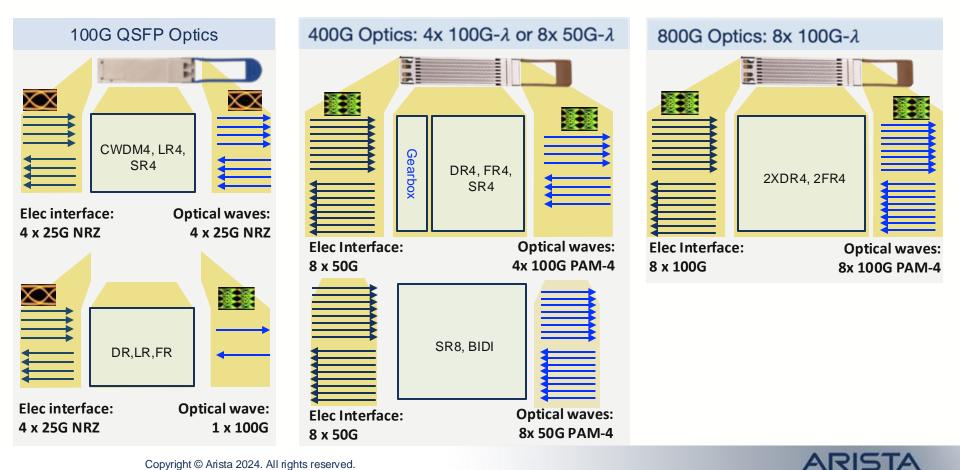

#### Serdes Speeds & Optical Speeds for 100G, 400G & 800G

# 400G

Confidential. Copyright © Arista 2024. All rights reserved.

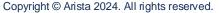

#### SMF 400G Optics

#### SMF 400G Optics Building Blocks

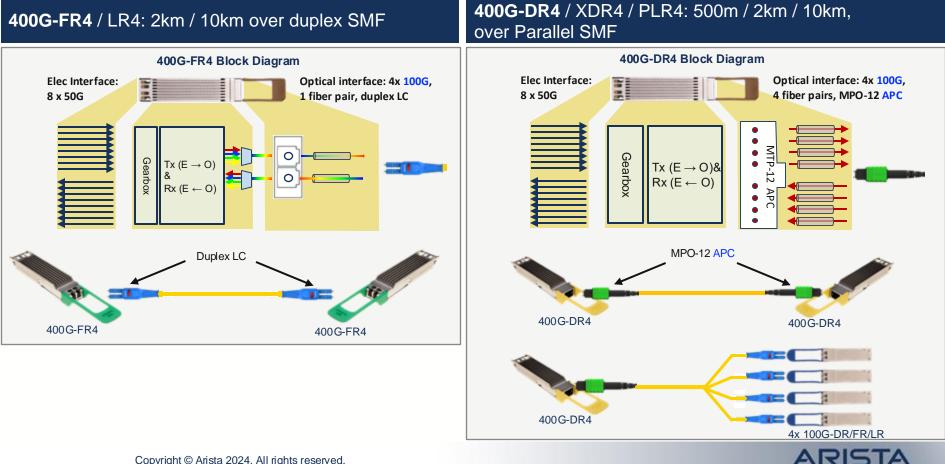

#### Upgrade duplex SMF from 100G to 400G

400G-FR4/LR4 uses the same fiber & connectors as 100G duplex-LC SMF Optics

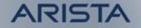

#### 400G-DR4/XDR4/PLR4 Optical Breakout to 4x100G

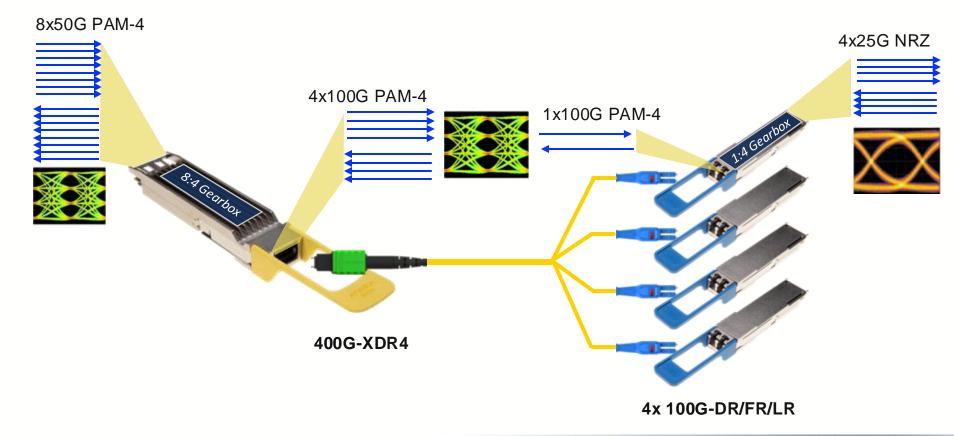

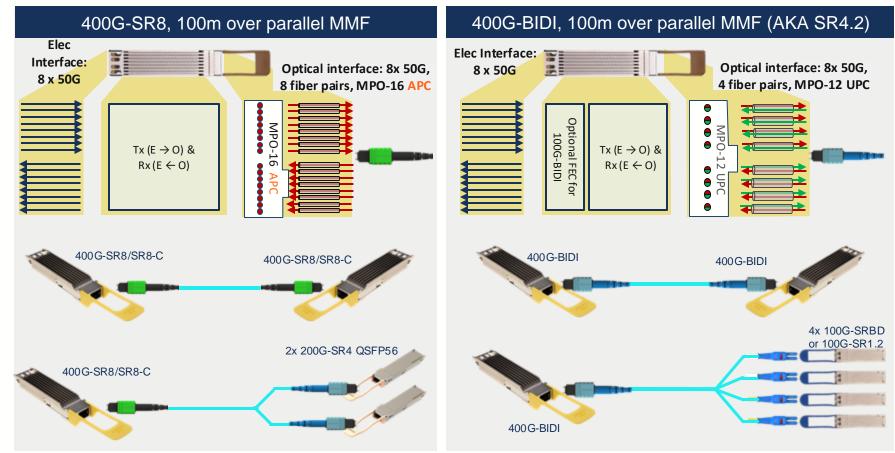

### MMF 400G Optics

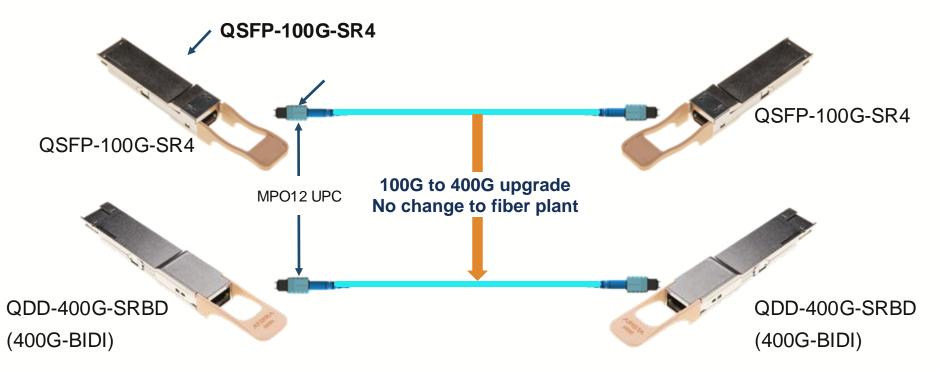

#### Upgrade MMF Networks from 100G to 400G with 400G-BIDI

# 400G-BIDI is the **ONLY** 400G Transceiver that uses EXACTLY the same fiber & connectors as 100G-SR4

ARISTA

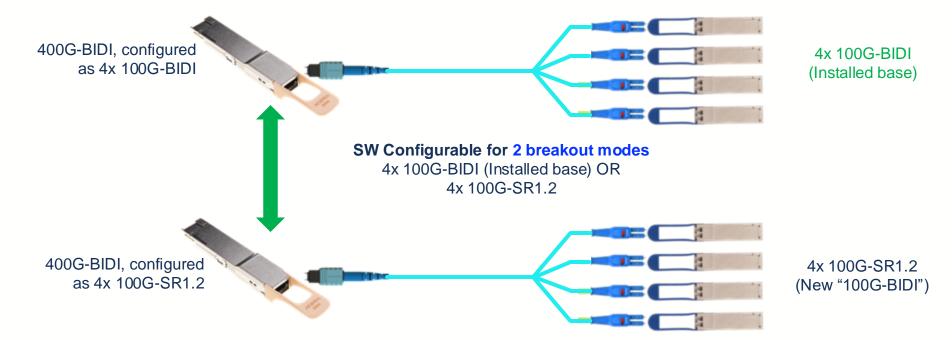

#### Flexible Breakout to 4x 100G with 400G-BIDI

#### 400G-BIDI is the **ONLY** 400G MMF Transceiver that enables simple 4x 100G Breakout

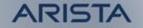

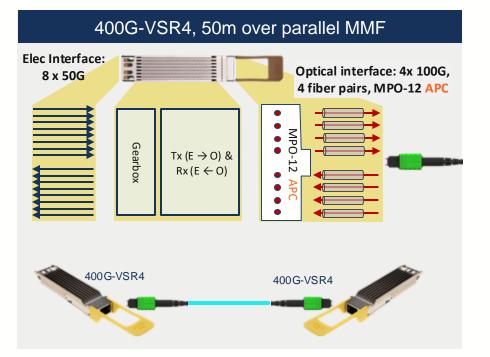

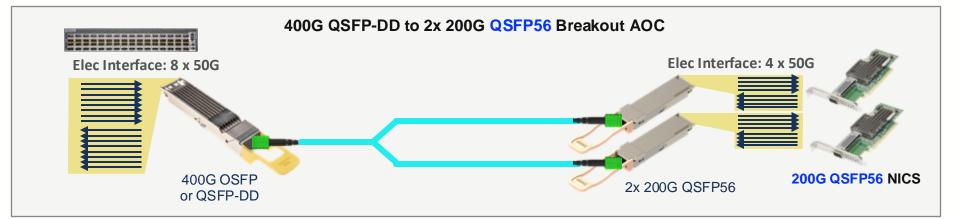

#### 400G-VSR4 for 400G Switch-to-NIC Connectivity

Key Application: 400G-8 switch ports to 400G-4 QSFP112 NIC

#### 400G-VSR4 is the **ONLY** 400G MMF Transceiver with 4x 100G Optical Channels for interop with 400G-SR4/VR4 QSFP112

### MMF 400G Optics Block Diagram

ARISTA

#### MMF 400G Optics Block Diagram

#### Note:

IEEE802.3 has standardized "400G-SR4" for 100m reach, and "400G-VR4" for 50m reach.

The Arista 400G-VSR4 will interop with both 400G-SR4 **and** 400G-VR4 optics over 50m

There are 50m reach optics on the market labelled as "400G-SR4"

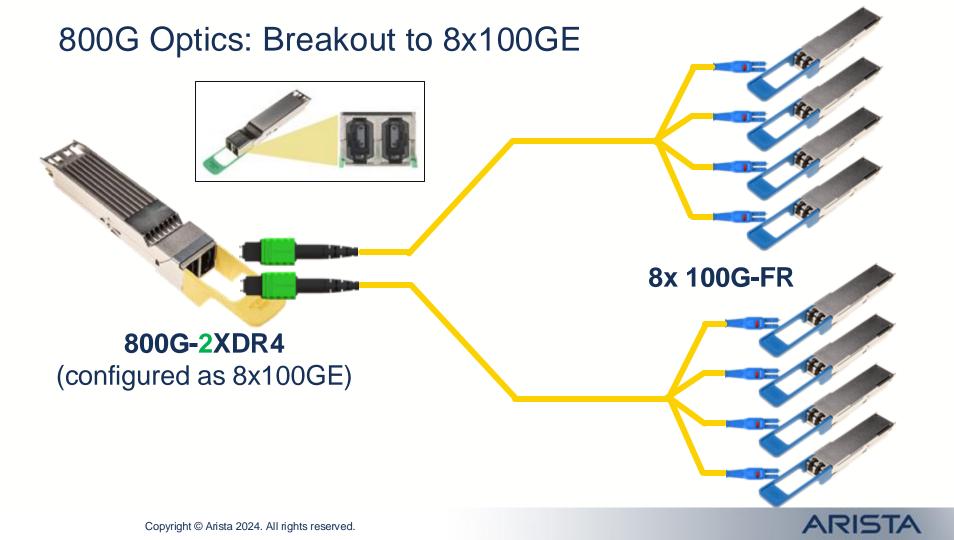

### 400G AOCs and Passive Copper Cables (DACs)

400G to 400G Active Optical Cables (AOCs)

400G to 400G DACs

Breakout to 2x200G QSFPs

Breakout to 4x100G-2 QSFPs

Breakout to 8x50G SFPs

#### 400G Copper Breakout Cables for Server Connections

100G-2 or 50G-1 QSFP NICs

#### 400G AOCs for NIC and GPU Connectivity

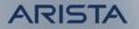

#### 400G-ZR+ Applications

Promoter

- 1. Amplified, using a **3<sup>rd</sup> party line system**: 500km 1000km+ depending on the mode of operation and line system design

- 2. Unamplified: 40km 60km reach, depending on fiber quality

# 800G

Confidential. Copyright © Arista 2024. All rights reserved.

# 400G to 800G Optics Transition

ARISTA

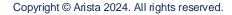

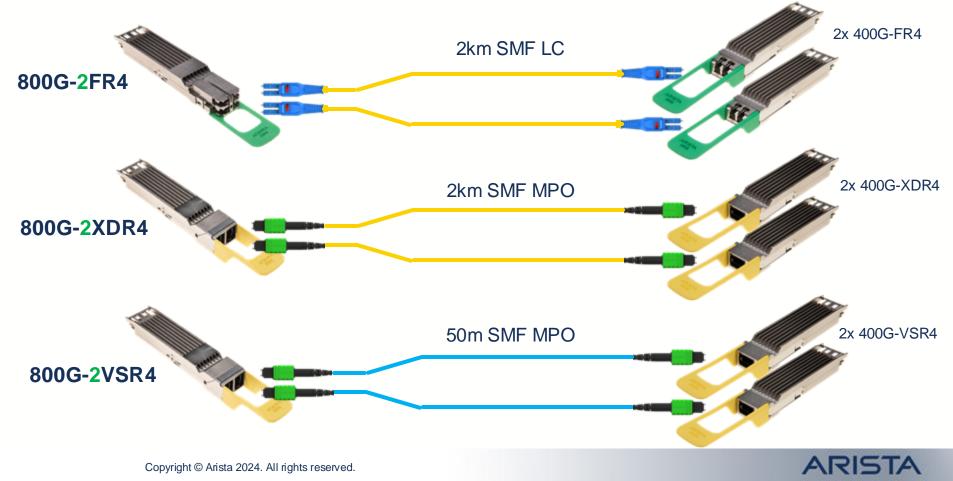

# 800G Optics = Double Density 400G Optics

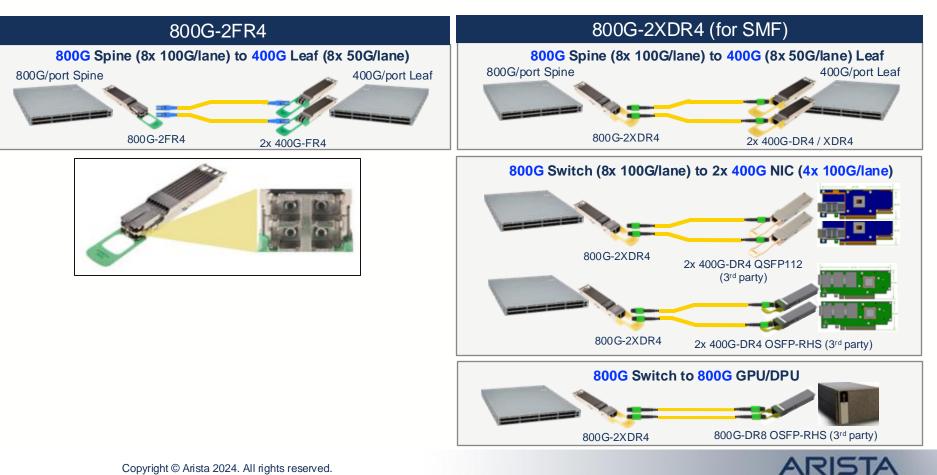

# SMF 800G Optics Applications Examples

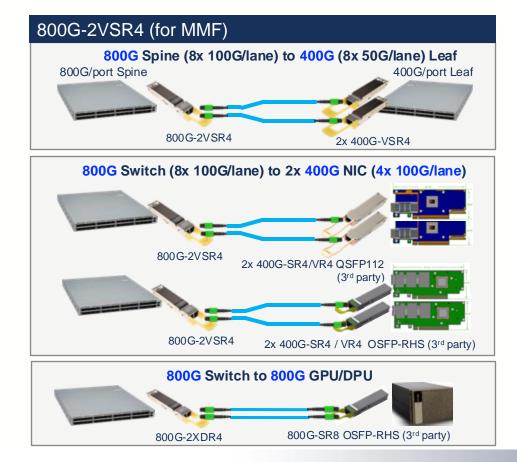

# MMF 800G Optics Applications Examples

# Beyond 800G

Confidential. Copyright © Arista 2024. All rights reserved.

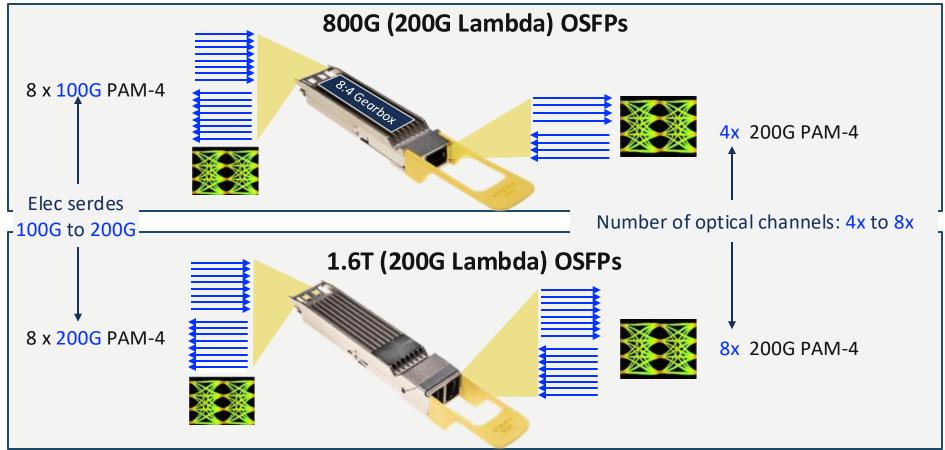

# 800G to 1.6T Optics Transition

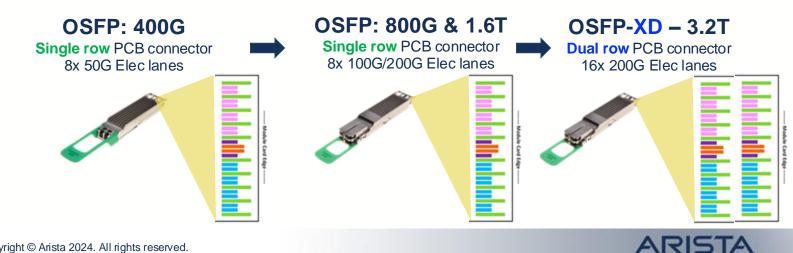

# **Optical Form-Factor Evolution**

Founding Member

**QSFP QSFP-DD: 400G QSFP-DD: 800G** Single row PCB connector **Dual row** PCB connector **Dual row** PCB connector 4x 25G Elec lanes 8x 50G Elec lanes 8x 100G Elec lanes

Founding Member

# **LPO** Optics

Confidential. Copyright © Arista 2024. All rights reserved.

# Linear-Drive Pluggable Optics (LPO) MSA

Founding Member

- Develops electrical and optical interoperability specifications for a diversity of high-density networking equipment and pluggable optical modules based on LPO technology

- Includes switches: NICs, and endpoints that include native Ethernet connectivity (such as GPUs)

- Ideal for high-speed, high-volume applications such as AI and highperformance computing

# Linear-Drive Pluggable Optics (LPO)

Founding Member

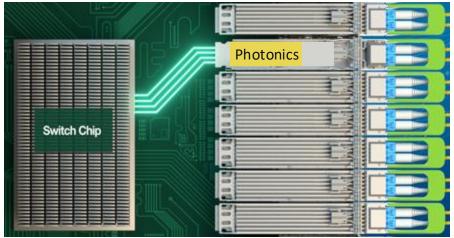

# Switch Chip

Traditional pluggable optical modules

### **LPO Modules**

- LPO means no DSP in the module

- Switch Silicon SerDes use advanced DSP technology

- Requires excellent system design and careful serdes tuning

- Switch Silicon already shipping

Founding Member

- → Significantly lower power consumption

- → Meets and exceeds link reliability requirements

- → Lower latency (vs. DSP-based solutions)

- → Lower module cost (vs. DSP-based solutions)

- → 100 Gb/s per lane operation extending to 200 Gb/s per lane

- → Enables a broad ecosystem of LPO module manufacturers and LPOenabled networking equipment

# Thank You

arista.com

Confidential. Copyright © Arista 2024. All rights reserved.

# References

https://www.arista.com/assets/data/pdf/Arista100G\_TC\_QA.pdf https://www.arista.com/assets/data/pdf/Datasheets/Arista-400G\_Optics\_FAQ.pdf https://www.arista.com/assets/data/pdf/Arista-800G-Transceivers-and-Cables-FAQ.pdf https://osfpmsa.org https://ethernettechnologyconsortium.org https://www.lpo-msa.org https://openzrplus.org/